数字电路实验-集成门电路的功能测试

一、实验目的

① 学会读集成电路的管脚图。

② 掌握逻辑门电路的符号与实物之间的对应关系。

③ 掌握各种门电路的逻辑符号、逻辑表达式、逻辑功能和逻辑实现,特别是与非门和异或门的逻辑功能。

④ 进一步熟悉数字技术实验装置使用方法。

二、实验器材

① KHD-2数字技术实验装置。

② 二踪示波器DC4322B 20HZ 一台。

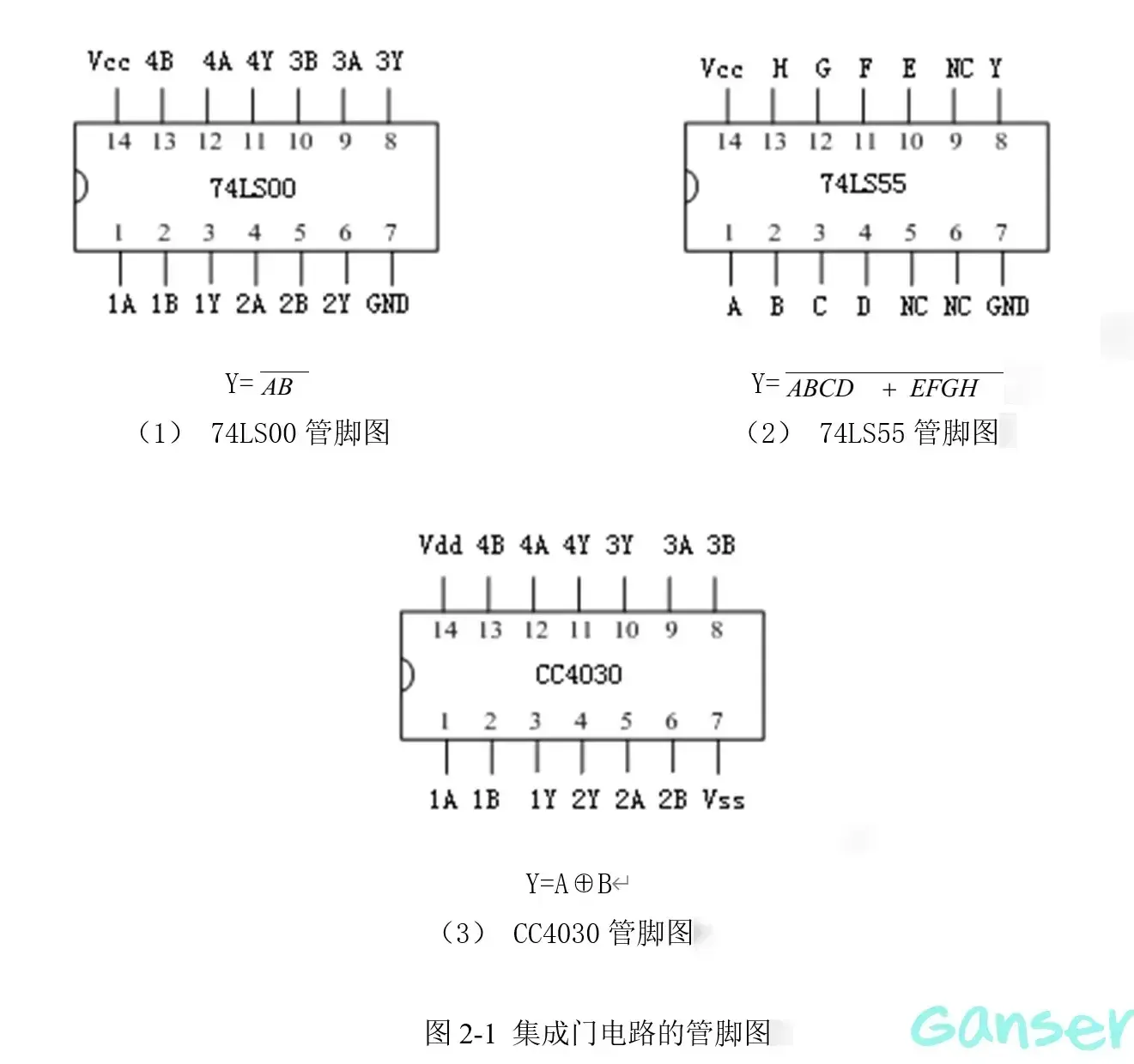

③ 器件 74LS00 2输入端四与非门 1片;74LS55 4-4输入与或非门 1片 ;CD4030 2输入端四异或门 1片 。 它们的管脚图如图2-1所示。

三、实验说明

选择实验用的集成电路按自己设计的实验接线图接好连线。特别注意Vcc及地线不能接错。线接好后经实验指导教师检查无误后方可通电实验。实验中改动接线须先断开电源,接好线后再通电实验。

四、预习要求

① 复习门电路工作原理及相应逻辑表达式。

② 熟悉所用集成电路的引脚位置及各引脚功能。

③ 熟悉双踪示波器的使用方法。

五、实验内容及步骤

5.1 与非门逻辑功能测试

① 选用二输入四与非门74LS00中的一个与非门,电源引脚接实验台+5V DC,输入引脚接逻辑开关(16个开关任选2个),输出引脚接发光二极管(16个发光二极管任选1个)。

② 将逻辑开关按表2.1置位,分别测输出电压及逻辑状态。

5.2 异或门逻辑功能测试

① 选二输入四异或门电路CC4030的一个异或门,电源引脚接实验台+5V DC,输入引脚接逻辑开关(16个开关任选2个),输出引脚接发光二极管(16个发光二极管任选1个)。

② 将逻辑开关按表2.2置位,将结果填入表中。

| 输入 | 输出 | ||

|---|---|---|---|

| A | B | Y | 电压(V) |

| 0 | 0 | 1 | 5 |

| 0 | 1 | 1 | 5 |

| 1 | 0 | 1 | 5 |

| 1 | 1 | 0 | 0 |

| A | B | Y | 电压(V) |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 5 |

| 1 | 0 | 1 | 5 |

| 1 | 1 | 0 | 0 |

5.3 与或非门逻辑功能测试

① 将4-4输入与或非门74LS55改为2-2输入使用。电源引脚接实验台+5V DC,输入引脚接逻辑开关(16个开关任选4个),输出引脚接发光二极管(16个发光二极管任选1个)。

② 自己设计操作功能表,将结果填入表中。

六、 实验报告要求

6.1 判断所测电路性能的好坏

解:74LS55真值表如下,仿真电路如下,所测仿真电路符合所学知识

| 输入 | 输出 | ||||

|---|---|---|---|---|---|

| A | B | C | D | Y | 电压(V) |

| 0 | 0 | 0 | 0 | 1 | 5 |

| 0 | 0 | 0 | 1 | 1 | 5 |

| 0 | 0 | 1 | 0 | 1 | 5 |

| 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 5 |

| 0 | 1 | 0 | 1 | 1 | 5 |

| 0 | 1 | 1 | 0 | 1 | 5 |

| 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 5 |

| 1 | 0 | 0 | 1 | 1 | 5 |

| 1 | 0 | 1 | 0 | 1 | 5 |

| 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 |

6.2 回答思考题

① TTL与非门输入端悬空为什么可以当作输入为“1”?

解:TTL与非门电路输入端悬空时,输入可看为高电平输入。因为TTL与非门的输入端是NPN三极管从发射极输入结构。基极有电阻接电源VCC,发射极可是多个,每个即是一个输入端,当输入悬空时,VCC电源电压通过电阻连到三极管基极,基极到输入端是PN结构,所以悬空时输入为高电平。不用的输入端可连接到电源电压VCC,这样即抗干扰有不影响与非运算,也可将不用的输入端和用的输入端连在一起当一个输入端用。

② 讨论TTL或非门闲置输入端的处置方法

解:TTL与非门电路多余输入端的处理有四种方法 :1、将多余输入端接高电平.即通过限流电阻与电源相连接。2、根据TTL门电路的输入特性可知,当外接电阻为大电阻时.其输入电压为高电平。这样可以把多余的输入端悬空.此时.输入端相当于外接高电平。3、通过大电阻到地,这也相当于输入端外接高电平。4、当TTL门电路的工作速度不高.信号源驱动能力较强.多余输入端也可与使用的输入端并联使用。

③ 上网搜索集成电路的封装形式有哪些?

解:SOP小外形封装、PGA插针网格阵列封装、BGA球栅阵列封装、DIP双列直插式封装

④ 简述TTL门电路和CMOS门电路的区别

解:① CMOS 是场效应管构成(单极性电路),TTL 为双极晶体管构成(双极性电路)

② COMS 的逻辑电平范围比较大(5~15V),TTL 只能在 5V 下工作

③ CMOS 的高低电平之间相差比较大、抗干扰性强,TTL 则相差小,抗干扰能力差

④ CMOS 功耗很小,TTL 功耗较大(1~5mA/ 门

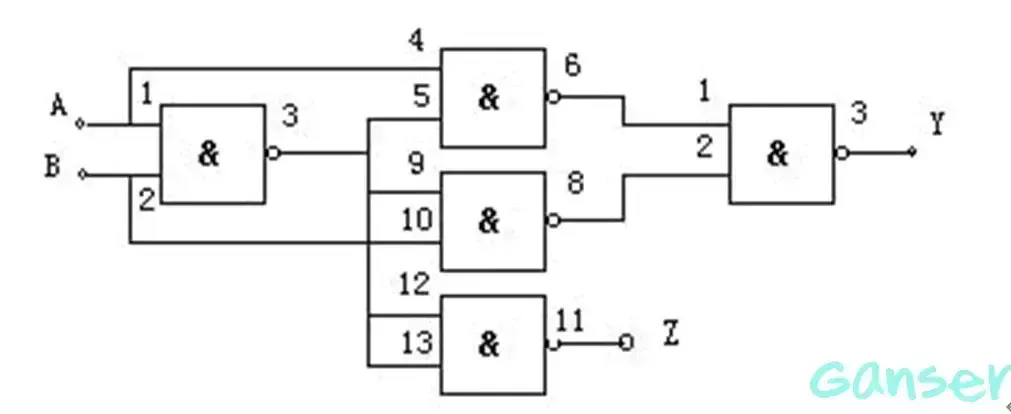

⑤ 逻辑电路的逻辑关系及逻辑表达式

| 输入 | 输出 | |

|---|---|---|

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| 输入 | 输出 | ||

|---|---|---|---|

| A | B | Y | Z |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 5 |

| 1 | 0 | 1 | 5 |

| 1 | 1 | 0 | 0 |

解:① Y=A⊕B

② Y=A⊕B Z=A•B